#### **FAST TRANSIENT RESPONSE LDO CONTROLLER**

## **General Description**

The AMS2115 is a single IC controller that drives an external N Channel MOSFET as a source follower to produce a fast transient response, low dropout voltage regulator. The fast transient load performance is obtained by eliminating expensive tantalum or bulk electrolytic output capacitors in the demanding modern microprocessor applications. Precision-trimmed adjustable and fixed output voltage version accommodates any required microprocessor application. By selecting the Nchannel MOSFET Rds(on) a very low dropout voltage can be achieve. A protection feature includes a high side current limit amplifier that activates a circuit to limit the FET gate drive. A shutdown pin turns off the gate drive and some internal circuits to reduce quiescent current. AMS2115 is offered in 8L SOIC and package.

#### **Features**

- Fast Transient Response

- Dropout Voltage Defined by FET Used

- Very Tight Load Regulation

- High Side Sense Current Limit

### **Applications**

- Microprocessor Supplies

- Video Card Supplies

- Low Voltage Logic Supplies

- GTL Termination

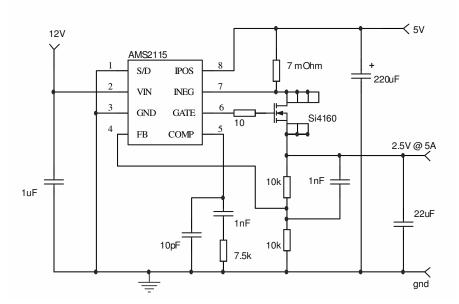

# Typical Application

# Pin Description (package)

| Pin# | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

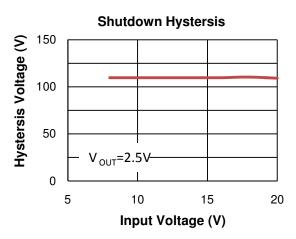

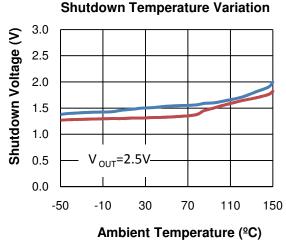

| 1    | S/D    | This is a shutdown pin that provides GATE drive latch-off capability. The pin is also the input to a comparator referenced to VREF (1.25V). When the pin pulls above VREF, the comparator latches the gate drive to the external MOSFET off. The comparator typically has 150mV of hysteresis and the Shutdown pin can be pulled low to reset the latch-off function. This pin provides overvoltage protection or thermal shutdown protection when driven from various resistor divider schemes. S/D pin is clamped at 2.5V.                                                                                                                                                                                                                      |

| 2    | VIN    | This is the input supply for the IC that powers the majority of internal circuitry and provides sufficient gate drive compliance for the external N-channel MOSFET. The typical supply voltage is 12 with 4.5 mA of quiescent current. The maximum operating VIN is 20V and the MOSFET at max. IOUT + 1.6V (worst-case VIN to GATE output swing).                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3    | GND    | Analog Ground. This pin is also the negative sense terminal for the internal 1.25V reference. Connect external feedback divider networks that terminate to GND and frequency compensation components that terminate to GND directly to this pin for best regulation and performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4    | FB     | This is the inverting input of the error amplifier for the adjustable voltage AMS 2115. The non-inverting input is tied to the internal 1.25V reference. Input bias current for this pin is typically – 3 µA flowing out of the pin. This pin is normally tied to a resistor divider network to set output voltage. Tie the top of the external resistor divider directly to the output voltage at the point of load for best regulation performance. This is the input of the error amplifier for the fixed voltage AMS 2115-X. The fixed voltage parts contain a divider network to set output voltage. The typical resistor divider current is 1 mA into the pin. Tie this pin directly to the output voltage for best regulation performance. |

| 5    | Comp   | The error amplifier output is used for external frequency compensation. Frequency compensation is generally performed with a series RC network to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6    | Gate   | This is the output of the error amplifier that drives N-channel MOSFETs with up to 5000pf of "effective" gate capacitance. The typical open-loop output impedance is 2 Ohms. When using low input capacitance MOSFETs (1500pF), a small gate resistor of 2 to 10 Ohms dampens high frequency ringing created by an LC resonance that is created by the MOSFET gate's lead inductance and input capacitance. The GATE pin delivers up to 50mA for a few hundred nanoseconds when slewing the gate of the N-channel MOSFET in response to output load current transients.                                                                                                                                                                           |

| 7    | INEG   | This is the negative sense terminal of the current limit amplifier. A small sense resistor is connected in series with the drain of the external MOSFET and is connected between the IPOS and INEG pins. A 50mV threshold voltage in conjunction with the sense resistor value sets the current limit level. The current sense resistor can be low value shut or can be made from a piece of PC board trace. If the current limit amplifier is not used tie the INEG and IPOS to power input voltage. This action disables the current limit amplifier.                                                                                                                                                                                           |

| 8    | IPOS   | This is the positive sense terminal of the current limit amplifier. Tie this pin directly to the main power input voltage from which the output voltage is regulated. This pin is also the input to a comparator that monitors the power input voltage and keeps the GATE voltage low until power input voltage is at least 1V. This prevents the external N Channel MOSFET to turn on before V power is on thus eliminating possible voltage spikes in the output voltage when powered up.                                                                                                                                                                                                                                                       |

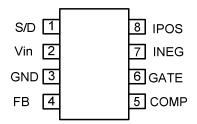

# **Pin Configuration**

# 8L SOIC SO Package (S) (Top View)

| Absolute Maximum Ratings (1)   |               |

|--------------------------------|---------------|

| Input Voltage                  | 20V           |

| Operating Junction Temperature | 40°C to 125°C |

| ESD                            | 2000V         |

| Storage Temperature Range      | 65°C to 150°C |

| Lead Temperature (10sec)       | 300°C         |

| Junction Temperature           | 150°C         |

| <b>Recommended Operating Conditions</b> | (2)           |

|-----------------------------------------|---------------|

| Input Voltage                           |               |

| Ambient Operating Temperature           | 40°C to 125°C |

| Thermal Information                     |               |

| SO-8 package <i>θ<sub>JA</sub></i>      | 130°C/W       |

#### **Electrical Characteristics**

$T_A=25C$ ,  $V_{IN}=12V$ , IPOS = INEG = 5V, SHDN = 0V unless otherwise noted.

| PARAMETER                                          | Device      | CONDITIONS                  | Min.                  | Тур.                | Max.      | Units    |

|----------------------------------------------------|-------------|-----------------------------|-----------------------|---------------------|-----------|----------|

| Supply Current (Isy)                               |             |                             |                       | 4.5                 | 7         | mA       |

| Reference Voltage (V <sub>REF</sub> )              | AMS2115     |                             | 1.238                 | 1.250               | 1.26      | V        |

| Output Voltage (V <sub>OUT</sub> )                 | AMS2115-1.5 |                             | 1.485                 | 1.500<br>1.0        | 1.51<br>5 | V<br>V   |

| Output Voltage (V <sub>OUT</sub> )                 | AMS2115-1.8 |                             | 1.782                 | 1.800               | 1.81      | V        |

| Output Voltage (V <sub>OUT</sub> )                 | AMS2115-2.5 |                             | 2.475                 | 2.500               | 2.52      | V        |

| Output Voltage (V <sub>OUT</sub> )                 | AMS2115-3.3 |                             | 3.267                 | 3.300               | 3.33      | V        |

| Output Voltage (V <sub>OUT</sub> )                 | AMS2115-5.0 |                             | 4.950                 | 5.000               | 5.05      | V        |

| Line Regulation                                    | AMS2115-XX  | 10V≤Vin≤20V                 |                       | 0.01                | 0.3       | %/V      |

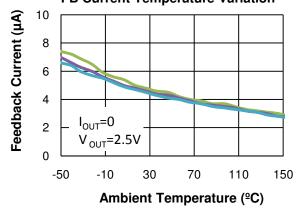

| Input Bias Current (Ifb)                           | AMS2115     | FB=V <sub>FB</sub>          |                       | -3.0                | -4.0      | μΑ       |

| OUT Divider Current                                | AMS2115-XX  | OUT=V <sub>OUT</sub>        |                       | 0.5                 | 1.0       | mA       |

| Gate Output Swing Low                              | AMS2115-XX  | I <sub>Gate</sub> =0mA      |                       | 0.1                 | 0.5       | V        |

| Gate Output Swing High                             | AMS2115-XX  | I <sub>Gate</sub> =0mA      | V <sub>IN</sub> -1.6V | V <sub>IN</sub> -1V |           | V        |

| IPOS+INEG Supply Current                           | AMS2115-XX  | 3V≤IPOS≤20V                 | 0.3                   | 0.625               | 1.0       | mA       |

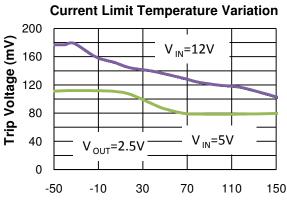

| Current Limit Threshold Voltage                    | AMS2115-XX  |                             |                       | 60<br><b>60</b>     |           | mV<br>mV |

| Current Limit Threshold Voltage<br>Line Regulation | AMS2115-XX  | 3V≤IPOS≤20V                 |                       | -0.20               | -0.50     | %/V      |

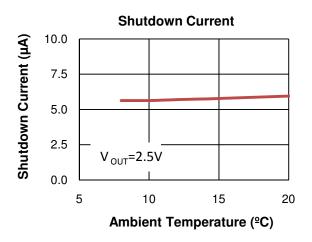

| Shut Down Current<br>(Input Shut Down – High)      | AMS2115-XX  | V <sub>Shutdown</sub> =2.0V |                       | 5.0                 | 8.0       | μА       |

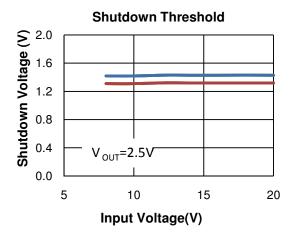

| Shut Down Input Logic<br>(Shut Down – Low)         | AMS2115-XX  | LOW (Regulator On)          |                       | 1.2                 | 1.4       | V        |

| Shut Down Input Logic<br>(Shut Down – High)        | AMS2115-XX  | High (Regulator Off)        | 2.0                   | 1.5                 |           | ٧        |

| Shut Down Hysteresis                               | AMS2115-XX  | From High to Low            |                       | 150                 |           | mV       |

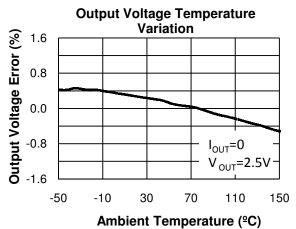

| Output Voltage TC (V <sub>OUT</sub> TC)            | AMS2115-XX  | ΔT=TA to 125℃               |                       | 30                  |           | ppm/°C   |

| Reference Voltage TC (V <sub>REF</sub> TC)         | AMS2115     | ΔT=TA to 125°C              |                       | 30                  |           | ppm/°C   |

Parameters identified with **boldface type** apply over the full operating temperature range. Notes:

Absolute maximum ratings indicate limits beyond which damage to the device may occur. For guaranteed specification and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed.

Line regulation is guaranteed up to the maximum input voltage XX represents all output voltages 1.

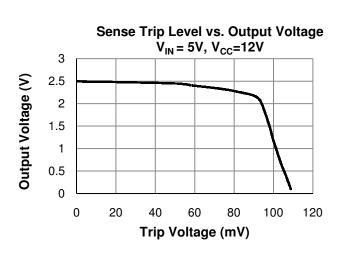

# Typical Performance Characteristics (T<sub>A</sub> = 25 ℃ unless otherwise specified)

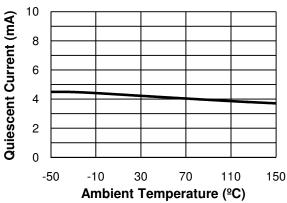

### Ambient Temperature (°C)

### **FB Current Temperature Variation**

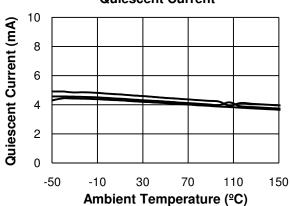

### **Quiescent Current**

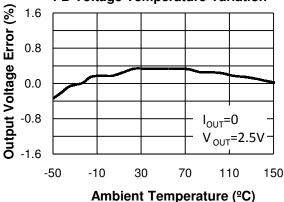

### **FB Voltage Temperature Variation**

#### **Quiescent Current**

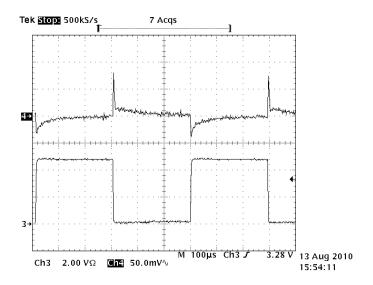

Load Transient RLoad from 10 Ohm to 0.5 Ohms Vin=5V, Vcc=12V, Vout=2.5V, Co=22 $\mu$ F

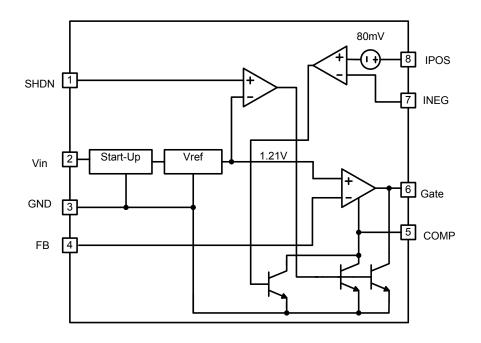

# **Functional Block Diagram**

#### **Device Summary**

The AMS2115 is a high speed, high current LDO controller designed to drive an external N-Channel MOSFET pass stage. An external resistor senses the load current to provide current limit. The output voltage is sensed through an external resistive divider that feeds the negative input to an internal transconductance error amplifier. The output of the error amplifier is pinned out so that external compensation can be adapted to the specific application. A separate high voltage Vcc input provides sufficient gate drive for low input voltage applications. The error amplifier regulates the output voltage by modulating the gate voltage of the external N Channel MOSFET. External compensation allows the converter to be stabilized with a low ESR ceramic output capacitor.

### **Application**

#### **Enable**

The LDO enable (S/D input pin) threshold is 1.2V with about 150mV of hysteresis. A high voltage applied to the S/D input enables the LDO controller.

#### **Fault Protection**

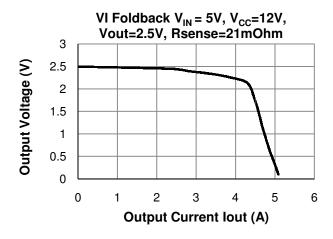

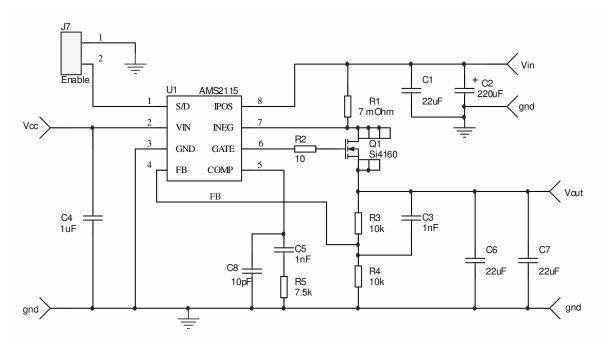

A current limit controller senses the pass transistor current through an external resistor tied to pins IPOS and INEG. The current limit threshold voltage is about 50mV. The initial current limit current limit point is 50mV divided by the external sense resistor.

Ilimit=

$$\frac{\text{Vos}}{\text{Rsense}} = \frac{50\text{mV}}{7\text{m}\Omega} = 7.14\text{A}$$

For an accurate current limit, the PCB traces for IPOS and INEG should connect to the resistor directly at the resistor in a Kelvin connection manner. This will prevent the drop associated with the high current PCB traces creating an error in the sense voltage.

For applications that require extremely low drop out, and do not require the current limit protection feature of the AMS2115, the current sense resistor can be eliminated and lpos and lneg shorted together.

#### **Output Capacitor**

A low ESR X5R or X7R type ceramic capacitor is sufficient for most applications. When selecting a ceramic output capacitor always consider the voltage rating and the capacitance voltage coefficient. For most applications the output capacitor required ranges from 10 to 22uF.

For applications with large load transients an additional capacitance may be required to keep the output voltage within reasonable limits during large load transients. In this case the required capacitance can be examined for the load application and load removal.

#### **Input Capacitor**

The bulk input capacitance required in the form of low cost high ESR aluminum or tantalum electrolytic capacitors will vary with the load transient requirements for the specific applications. Small low ESR ceramic input capacitors ranging from 10 to 22uF placed close to the input of the LDO are typically a sufficient compliment to the bulk capacitance of the converter feeding the input to this LDO.

#### Feedback Resistor Selection

The LDO controller uses a 1.25V reference voltage at the positive terminal of the internal error amplifier. To set the output voltage a programming resistor form the feedback node to ground must first be selected (R2, R3 of figure 4). A  $10k\Omega$  resistor is a good selection for a programming resistor. A higher value could result in an excessively sensitive feedback node while a lower value will draw more current and degrade the light load efficiency. The equation for selecting the voltage specific resistor is:

$$R2 = \left(\frac{\text{Vout}}{\text{Vref}} - 1\right) \cdot R3 = \left(\frac{2.5 \text{V}}{1.25 \text{V}} - 1\right) \cdot 10 \text{k}\Omega = 10 \text{k}\Omega$$

Table 2. Feedback Resistor values

| Vout (V) | R2 (kΩ)<br>(R3=10kΩ) |

|----------|----------------------|

| 2.5      | 10.0                 |

| 5.0      | 30.9                 |

| 3.3      | 16.5                 |

## Compensation

External compensation is comprised of a lead-lag network (R5, C5, and C8 of the schematic shown figure 3) tied to the output of the internal error amplifier.

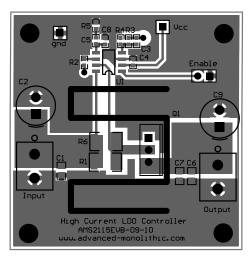

Figure 1: AMS2115 Evaluation Board Top Side

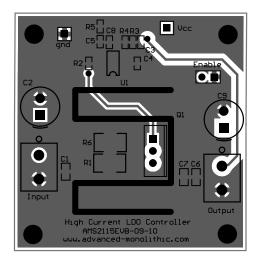

Figure 2: AMS2115 Evaluation Board Bottom Side

Figure 3: AMS2115 Evaluation Board Schematic

Table 3: AMS2115 Evaluation Board Bill of Materials

| Comp | onent      | Value                         | Manufacturer | Manufacturer Part Number |

|------|------------|-------------------------------|--------------|--------------------------|

| C    | 2          | 220μF, Electrolytic           |              |                          |

| C1,C | 6,C7       | 22μF, 10V, X5R, 0805, Ceramic | Taiyo Yuden  | LMK212BJ226MG-T          |

| C    | 74         | 1μF                           |              |                          |

| R1   | ,R6        | 7mΩ 1/4Watt 1206              | Vishay/Dale  | WSLC007TR                |

|      | 2.5V       | 30.9kΩ, 0.1W, 0603 1%         | Various      | CRCW0603xxKxFKEA         |

| R3   | 5V         | 88.7kΩ, 0.1W, 0603 1%         | Various      | CRCW0603xxKxFKEA         |

|      | 1.2V       | 113kΩ, 0.1W, 0603 1%          | Various      | CRCW0603xxKxFKEA         |

| F    | <b>?</b> 4 | 10.0kΩ, 0.1W, 0603 1%         | Various      | CRCW060310K0FKEA         |

| Q1   |            | Si4160                        | Diodes Inc.  |                          |

| L    | J1         | LDO Controller                | AMS          | AMS2115 SO8              |

# **Ordering Information**

| Device                     | Package | Voltage Tolerance (V <sub>OUT</sub> ) |

|----------------------------|---------|---------------------------------------|

| AMS2115S <sup>(1)(2)</sup> | SO-8    | ±2%                                   |

#### Notes:

- 1. Available in tape and reel only. A reel contains 2,500 devices.

- 2. Available in lead-free package only. Device is fully WEEE and RoHS compliant

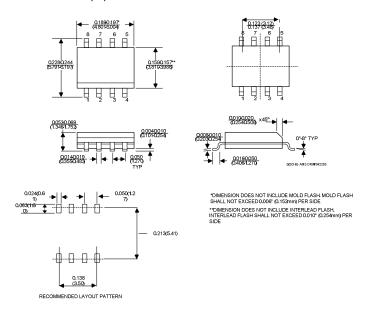

### **Outline Drawing and Landing Pattern**

Package dimensions are inches (millimeters) unless otherwise noted.

### 8 LEAD SOIC PLASTIC PACKAGES (S)